# Compiler Support for Machine-Independent Parallelization of Irregular Problems

Reinhard von Hanxleden

CRPC-TR94494-S December 1994

> Center for Research on Parallel Computation Rice University P.O. Box 1892 Houston, TX 77251-1892

#### RICE UNIVERSITY

# Compiler Support for Machine-Independent Parallelization of Irregular Problems

by

#### Reinhard von Hanxleden

A THESIS SUBMITTED

IN PARTIAL FULFILLMENT OF THE

REQUIREMENTS FOR THE DEGREE

### **Doctor of Philosophy**

APPROVED, THESIS COMMITTEE:

Ken Kennedy, Noah Harding Professor, Chair Department of Computer Science Rice University

John Mellor-Crummey, Faculty Fellow Department of Computer Science Rice University

Mary Wheeler, Noah Harding Professor Department of Computational and Applied Mathematics Rice University

Charles Koelbel, Research Scientist Center for Research on Parallel Computation Rice University

Ridgway Scott, Professor of Computer Science and of Mathematics University of Houston

Houston, Texas December, 1994

# Compiler Support for Machine-Independent Parallelization of Irregular Problems

#### Reinhard von Hanxleden

#### Abstract

Data-parallel languages, such as HIGH PERFORMANCE FORTRAN or FORTRAN D, provide a machine-independent data-parallel programming paradigm in which the applications programmer uses a dialect of a sequential language annotated with high-level data-distribution directives. Identifying parallelism in data-parallel applications typically is straightforward, but making efficient use of this parallelism for irregular applications, such as molecular dynamics or unstructured meshes, is a challenge due to the limited compile-time knowledge about data access patterns.

This dissertation establishes the thesis that spatial locality of the underlying problems can be used as a basis of compiler support for parallelizing such applications. The work done for supporting this thesis and for parallelizing applications in general can be divided into three parts, which correspond to different aspects of parallelizing compilers for different architectures. Value-based mappings express the spatial locality characteristics of an application and assist the compiler in computing a distribution with both a balanced computational workload and high data access locality. The GIVE-N-TAKE data-flow framework is an extension of Partial Redundancy Elimination particularly well suited to advanced code-placement tasks such as communication generation. Loop flattening is a code transformation to overcome SIMD specific control flow limitations when executing nested loops with varying inner loop bounds, which are typical for irregular problems.

To illustrate this thesis, the FORTRAN 77D compiler at Rice University has been extended with value-based alignments and distributions, a communication placement mechanism based on the GIVE-N-TAKE data-flow framework, and general infrastructure for handling irregular subscripts. This dissertation describes the techniques involved in these extensions and provides experimental results for various irregular applications compiled for a distributed-memory architecture.

# Acknowledgments

This dissertation and the excellent research environment in which the underlying work was conducted would not exist without my advisor, Ken Kennedy. He was most supportive professionally and understanding in personal issues, and he gave advice when it counted. Ridgway Scott, whose seminar on parallel computation at Penn State got me in touch with this matter originally, not only was excellent in advising my M.Sc. thesis, along with my academic advisor, Georg Schnitger; but he and his family (and his pool) convinced me that Houston, Texas, is indeed a good place to live. Together with John Mellor-Crummey, Chuck Koelbel, and Mary Wheeler they constituted a critical, helpful, and uniquely stimulating thesis committee. I would also like to thank IBM corp. for providing me with a generous fellowship, and the National Aeronautics and Space Administration and the National Science Foundation, who supported this work under grant #ASC-9349459.

Terry Clark was the one who provided me with most insights on real-world scientific programs and proved to be an excellent collaborator. Joel Saltz and Raja Das were inspiring partners for discussing the parallelization of irregular applications and, together with other members of their group, were of critical importance for the FORTRAN D implementation efforts. Special thanks also go to Seema Hiranandani and Chau-Wen Tseng, who developed the original FORTRAN D compiler, to Paul Havlak, whose symbolic analysis proved extremely valuable, and to the other D System developers, who made this implementation possible. Scott Baden, whose thesis raised my first interest in irregular applications, has since then continuously influenced my thinking on this matter.

My cheerful office mates Nat McIntosh and Uli Kremer never let me down; Nat in particular gave countless insights along the path to Unix wisdom. Kevin Cureton saved the world whenever it was broken and proved an able master of monster makefiles. Debbie Campbell mercifully took up the cause of getting my technical writing in shape. Our staff was always competent and extremely helpful; in particular, Ivy Jorgensen, Ken Marshall, and Sean Starke never tired of answering questions and keeping things running smoothly.

All of these people have not only improved the research environment, but also enriched life at Rice in general. However, there is also a long list of other characters I am indebted to for making graduate school the experience it has been. A very incomplete subset includes Ervan, organizer of canoeing, stargazing, tubing, kayaking, hiking, sailing and road trips; Rosana and Pete, who will hopefully keep up the brewing in DC; Steph and Jerry, happy hot-tub hosts whenever it got chilly; Don, whose bike was very difficult to hang on to; Saniya and Karim, whose Tunisian food was simply the best; Gregor and Kay, fine hiking partners on those winter treks in northern Germany; and David, who was not discouraged by tents ripping away if we "were lucky with the weather." And there is, of course, the Valhalla crew.

My deepest gratitude, however, is reserved for those to whom this thesis is dedicated: my parents and my wife.

# Contents

|          | Abs                  | tract     |                                                               | i  |

|----------|----------------------|-----------|---------------------------------------------------------------|----|

|          | Ack                  | gments    | ii                                                            |    |

|          | List                 | of Illus  | strations                                                     | Х  |

| 1        | $\mathbf{Int}$       | rodu      | ction                                                         | 1  |

|          | 1.1                  | Irregu    | lar Problems                                                  | 1  |

|          | 1.2 Previous Results |           |                                                               |    |

|          |                      | 1.2.1     | The inspector-executor paradigm                               | 9  |

|          |                      | 1.2.2     | Compilation systems for irregular problems                    | 4  |

|          |                      | 1.2.3     | Mapping arrays and mapping functions                          | Ę  |

|          |                      | 1.2.4     | Value-based mappings                                          | 6  |

|          |                      | 1.2.5     | Communication analysis                                        | 6  |

|          |                      | 1.2.6     | Evaluation                                                    | 7  |

|          | 1.3                  | The T     | hesis                                                         | 7  |

| <b>2</b> | Va                   | lue-B     | ased Mappings                                                 | 9  |

|          | 2.1                  | Value-    | -Based Locality                                               | 10 |

|          |                      | 2.1.1     | Molecular dynamics - An example for value-based distributions | 11 |

|          |                      | 2.1.2     | Unstructured meshes - An example for value-based alignments   | 13 |

|          | 2.2                  | Implie    | cations of Value-Based Mappings                               | 18 |

|          |                      | 2.2.1     | Specification and state                                       | 19 |

|          |                      | 2.2.2     | Storing value-based distributed data                          | 19 |

|          |                      | 2.2.3     | Translating name spaces                                       | 20 |

|          |                      | 2.2.4     | Communication generation                                      | 20 |

|          |                      | 2.2.5     | A bootstrapping problem                                       | 20 |

|          | 2.3                  | The C     | Compiler's Perspective                                        | 21 |

|          |                      | 2.3.1     | The input language                                            | 21 |

|          |                      | $2\ 3\ 2$ | When to distribute and align                                  | 22 |

| 3 | Ba             | lance                        | d Code Placement with Give-N-Take                      | 24 |  |  |  |  |  |

|---|----------------|------------------------------|--------------------------------------------------------|----|--|--|--|--|--|

|   | 3.1            | J                            |                                                        |    |  |  |  |  |  |

|   | 3.2            | A Coo                        | de Placement Example Problem: Communication Generation | 26 |  |  |  |  |  |

|   |                | 3.2.1                        | The model                                              | 29 |  |  |  |  |  |

|   |                | 3.2.2                        | Previous work                                          | 31 |  |  |  |  |  |

|   | 3.3            | The C                        | Give-N-Take Framework                                  | 33 |  |  |  |  |  |

|   |                | 3.3.1                        | Communication placement with Give-N-Take               | 33 |  |  |  |  |  |

|   |                | 3.3.2                        | Correctness and optimality                             | 34 |  |  |  |  |  |

|   |                | 3.3.3                        | Zero-trip loop constructs                              | 36 |  |  |  |  |  |

|   |                | 3.3.4                        | The Interval-Flow Graph                                | 39 |  |  |  |  |  |

|   |                | 3.3.5                        | Traversal orders and neighbor relations                | 43 |  |  |  |  |  |

|   | 3.4            | Give-]                       | N-Take Equations                                       | 45 |  |  |  |  |  |

|   |                | 3.4.1                        | Initial variables                                      | 45 |  |  |  |  |  |

|   |                | 3.4.2                        | Propagating consumption                                | 47 |  |  |  |  |  |

|   |                | 3.4.3                        | Blocking consumption                                   | 48 |  |  |  |  |  |

|   |                | 3.4.4                        | Placing production                                     | 49 |  |  |  |  |  |

|   |                | 3.4.5                        | Result variables                                       | 5( |  |  |  |  |  |

|   | 3.5            | ng the Equations             | 51                                                     |    |  |  |  |  |  |

|   |                | 3.5.1                        | The constraints                                        | 51 |  |  |  |  |  |

|   |                | 3.5.2                        | The algorithm                                          | 53 |  |  |  |  |  |

|   |                | 3.5.3                        | Before vs. After problems                              | 55 |  |  |  |  |  |

|   |                | 3.5.4                        | A note on synthetic nodes                              | 55 |  |  |  |  |  |

|   | 3.6            | Sumn                         | nary                                                   | 56 |  |  |  |  |  |

|   |                |                              |                                                        |    |  |  |  |  |  |

| 4 | $\mathbf{Irr}$ | egula                        | r Computations on SIMD architectures                   | 58 |  |  |  |  |  |

|   | 4.1            | Langu                        | ıages                                                  | 59 |  |  |  |  |  |

|   | 4.2            | 2 Example of Loop Flattening |                                                        |    |  |  |  |  |  |

|   | 4.3            | Gener                        | al Loop Flattening                                     | 63 |  |  |  |  |  |

|   |                | 4.3.1                        | Loop normalization                                     | 63 |  |  |  |  |  |

|   |                | 4.3.2                        | The transformation                                     | 65 |  |  |  |  |  |

|   |                | 4.3.3                        | Optimizations                                          | 67 |  |  |  |  |  |

|   | 4.4            | Loop                         | Flattening from the Compiler's Perspective             | 67 |  |  |  |  |  |

| 5 | Im             | $\mathbf{plem}_{\mathbf{q}}$ | entation Experience                                    | 71 |  |  |  |  |  |

|   | 5.1            | Overv                        | iew                                                    | 71 |  |  |  |  |  |

|   | 5.2                    | The A  | nalysis Phase                                        |

|---|------------------------|--------|------------------------------------------------------|

|   |                        | 5.2.1  | Symbolic analysis                                    |

|   |                        | 5.2.2  | The regular part of FORTRAN D compiler               |

|   |                        | 5.2.3  | The data-flow universe for communication analysis 76 |

|   |                        | 5.2.4  | Communication analysis                               |

|   |                        | 5.2.5  | Inspectors                                           |

|   |                        | 5.2.6  | Executors                                            |

|   | 5.3                    | The C  | Sode-Generation Phase                                |

|   |                        | 5.3.1  | The regular compiler                                 |

|   |                        | 5.3.2  | Value-based mappings                                 |

|   |                        | 5.3.3  | Trace arrays                                         |

|   |                        | 5.3.4  | Inspectors                                           |

|   |                        | 5.3.5  | Communication statements                             |

|   |                        | 5.3.6  | Reduction initialization                             |

|   |                        | 5.3.7  | The actual computation                               |

|   |                        | 5.3.8  | Executors                                            |

|   |                        | 5.3.9  | Dynamically allocated arrays                         |

|   |                        | 5.3.10 | Final notes on the compiler output                   |

|   | 5.4                    | An Ol  | oject-Oriented Design                                |

|   |                        | 5.4.1  | Overview                                             |

|   |                        | 5.4.2  | The classes                                          |

| 6 | $\mathbf{E}\mathbf{x}$ | perin  | nental Results 102                                   |

|   | 6.1                    | Value- | vs. Index-Based Mappings                             |

|   |                        | 6.1.1  | The molecular dynamics kernel                        |

|   |                        | 6.1.2  | The unstructured mesh kernel                         |

|   |                        | 6.1.3  | A sparse matrix computation                          |

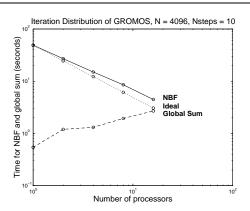

|   |                        | 6.1.4  | Full Gromos                                          |

|   | 6.2                    | The E  | fficacy of Loop Flattening                           |

|   |                        | 6.2.1  | The application                                      |

|   |                        | 6.2.2  | The hardware used                                    |

|   |                        | 6.2.3  | Implementation experience                            |

|   |                        | 6.2.4  | The input data                                       |

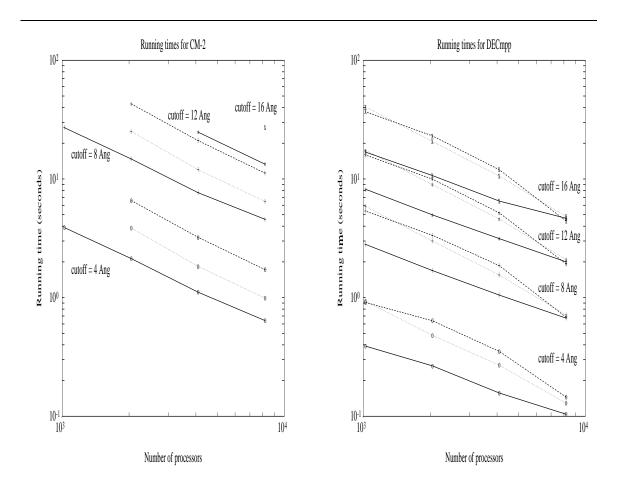

|   |                        | 6.2.5  | The results                                          |

|   |                        | 6.2.6  | Interpretation                                       |

| 7            | Ba  | ${f ckgro}$ | ound and Related Work                            | 124        |

|--------------|-----|-------------|--------------------------------------------------|------------|

|              | 7.1 | Tools       |                                                  | 124        |

|              |     | 7.1.1       | Tools based on spatial decomposition             | 124        |

|              |     | 7.1.2       | Tools based on access patterns                   | 126        |

|              | 7.2 | The C       | Compiler                                         | 127        |

|              |     | 7.2.1       | Parallel compilation systems                     | 127        |

|              |     | 7.2.2       | FORTRAN D                                        | 127        |

|              | 7.3 | The C       | Operating System                                 | 128        |

|              | 7.4 | The E       | Hardware                                         | 129        |

|              |     | 7.4.1       | Low latency                                      | 129        |

|              |     | 7.4.2       | General routing facilities                       | 129        |

|              |     | 7.4.3       | Decoupling of control flow on SIMD architectures | 129        |

|              |     | 7.4.4       | Fast scan operations                             | 130        |

| 8            | Su  | mmaı        | ry & Open Issues                                 | 131        |

|              | Bil | oliogr      | aphy                                             | <b>134</b> |

| $\mathbf{A}$ | Pro | oofs o      | of Correctness for GIVE-N-TAKE                   | 150        |

|              | A.1 | Proof       | of correctness of the data-flow equations        | 150        |

|              |     | A.1.1       | Balance                                          | 151        |

|              |     | A.1.2       | Safety                                           | 162        |

|              |     | A.1.3       | Sufficiency                                      | 163        |

|              | A.2 | Proof       | of correctness of the algorithm                  | 169        |

# Illustrations

| 2.1  | Sequential version of the Non-Bonded Force kernel nbf                  | 12 |

|------|------------------------------------------------------------------------|----|

| 2.2  | BLOCK mapping of an SOD system                                         | 13 |

| 2.3  | FORTRAN D version of the Non-Bonded Force kernel                       | 14 |

| 2.4  | Value-based mapping of atoms along just one dimension                  | 15 |

| 2.5  | Value-based mapping of atoms along all three dimensions                | 15 |

| 2.6  | FORTRAN D kernel of a sweep over the edges of an unstructured mesh.    | 16 |

| 2.7  | Example mesh with four nodes and five edges                            | 17 |

| 2.8  | Syntax of the value-based mapping directive                            | 22 |

| 3.1  | An instance of the communication placement problem                     | 27 |

| 3.2  | Possible communication placements                                      | 28 |

| 3.3  | A potentially illegal instance of the communication placement problem. | 30 |

| 3.4  | Example of a code with local definitions of potentially non-owned      |    |

|      | data (left), and a corresponding placement of global WRITES (right).   | 32 |

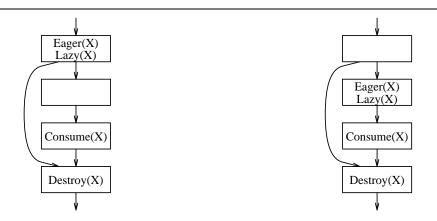

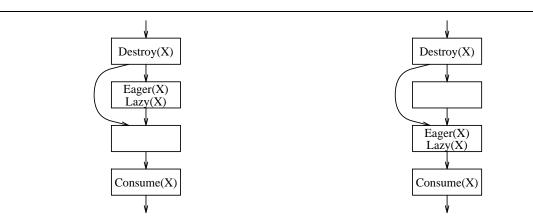

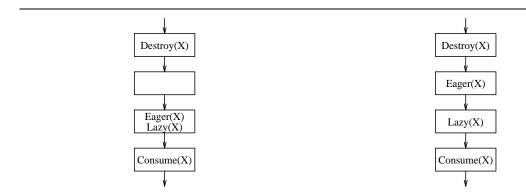

| 3.5  | Left: unbalanced production. Right: possible solution obeying          |    |

|      | correctness criterion C1                                               | 35 |

| 3.6  | Left: unsafe production. Right: possible solution obeying C2           | 35 |

| 3.7  | Left: insufficient production. Right: possible solution obeying C3     | 35 |

| 3.8  | Left: redundant production. Right: possible solution obeying O1        | 37 |

| 3.9  | Left: too many producers. Right: possible solution obeying O2          | 37 |

| 3.10 | Left: too late production. Right: possible solution obeying O3         | 37 |

| 3.11 | Left: too early production. Right: possible solution obeying O3'       | 38 |

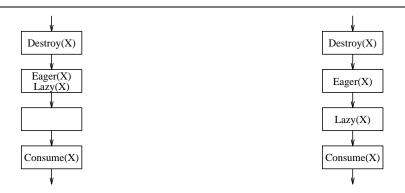

| 3.12 | Example code                                                           | 41 |

| 3.13 | Corresponding flow graph                                               | 42 |

| 3.14 | GIVE-N-TAKE equations                                                  | 46 |

| 3.15 | The code annotated with communication statements                       | 52 |

| 3.16 | Algorithm $GiveNTake$ computing an Eager/Lazy code placement           | 54 |

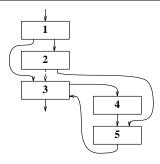

| 3.17 | Flow graph containing a jump into a loop                               | 56 |

| 4.1  | Original loop nest Example                                                              |

|------|-----------------------------------------------------------------------------------------|

| 4.2  | Example in F77D                                                                         |

| 4.3  | Example in F77 <sub>MIMD</sub>                                                          |

| 4.4  | MIMD execution trace for Example loop                                                   |

| 4.5  | Example in F90 <sub>SIMD</sub>                                                          |

| 4.6  | Execution trace for unflattened example loop                                            |

| 4.7  | Example in flattened F90 <sub>SIMD</sub>                                                |

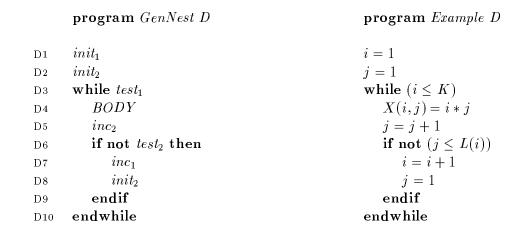

| 4.8  | Generic loop nest GenNest (left) and corresponding Example (right). 65                  |

| 4.9  | GenNest/Example, with guard variables                                                   |

| 4.10 | GenNest/Example, after flattening                                                       |

| 4.11 | Operational proof of equivalence of unflattened GenNest B, flattened                    |

|      | GenNest $C$ , and optimized $GenNest D$                                                 |

| 4.12 | GenNest/Example, flattened and optimized                                                |

| 4.13 | GenNest/Example after further optimization                                              |

|      |                                                                                         |

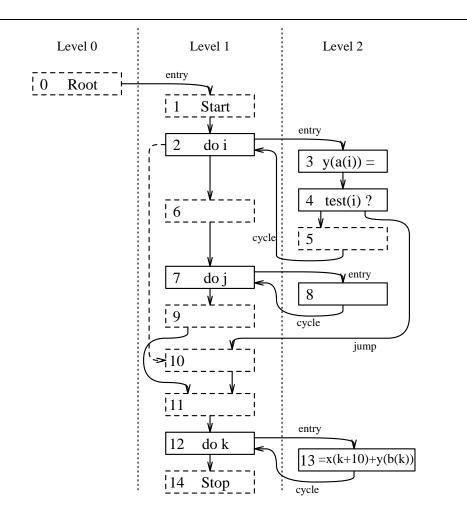

| 5.1  | Slightly simplified output of FORTRAN D compiler for nbf                                |

| 5.2  | Slightly simplified output of FORTRAN D compiler for nbf, continued. 74                 |

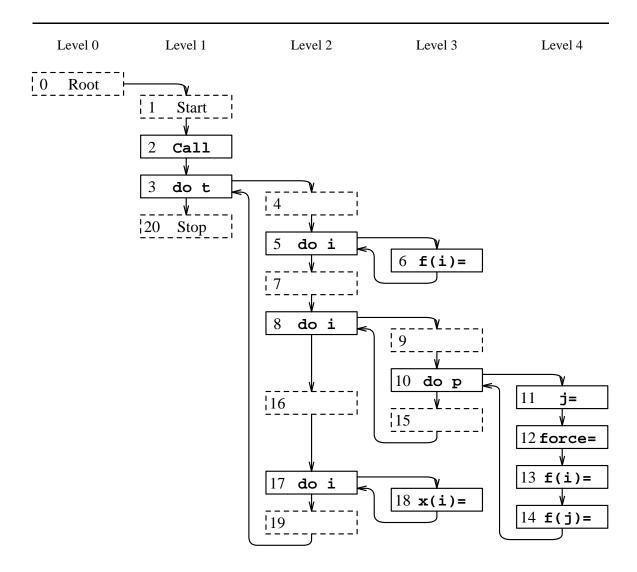

| 5.3  | Flow graph $G$ of nbf program                                                           |

| 5.4  | Description of the GIVE-N-TAKE-universe used for communication                          |

|      | placement                                                                               |

| 5.5  | The information that is computed for each node $n \in \mathbb{N}$ 79                    |

| 5.6  | Initializations of $TAKE_{init}$ , $STEAL_{init}$ , and $GIVE_{init}$ for the placement |

|      | of Read, Write, and Add communication operations 80                                     |

| 5.7  | The nbf program after compilation by the Fortran D compiler,                            |

|      | Part 1 of 3                                                                             |

| 5.8  | The nbf program after compilation by the FORTRAN D compiler,                            |

|      | Part 2 of 3                                                                             |

| 5.9  | The nbf program after compilation by the Fortran D compiler,                            |

|      | Part 3 of 3                                                                             |

| 5.10 | Main loop nest of the mesh kernel                                                       |

| 5.11 | Main loop nest of mesh kernel, output of FORTRAN D compiler with                        |

|      | communication and inspection body                                                       |

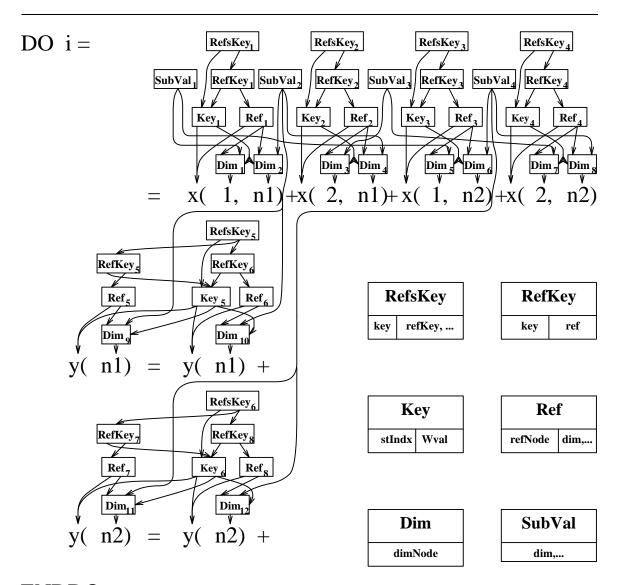

| 5.12 | C++ classes for constructing the communication data-flow universe 98                    |

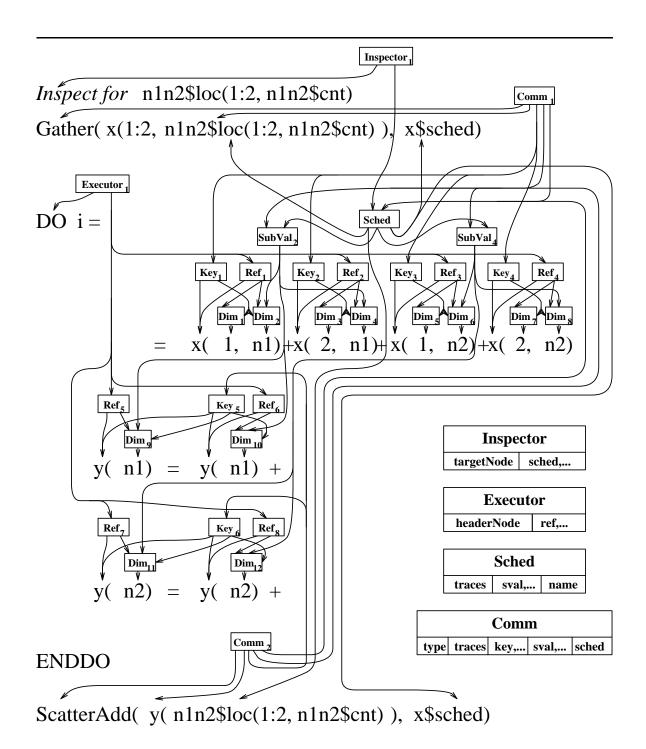

| 5.13 | C++ classes for placing communication statements, inspectors, and                       |

|      | executors                                                                               |

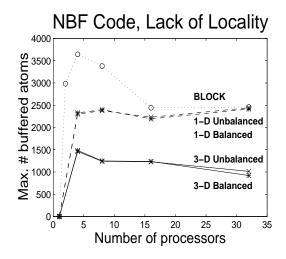

| 6.1  | The number of communicated data for nbf                    | 105 |

|------|------------------------------------------------------------|-----|

| 6.2  | The fraction of maximum floating point operations for nbf  | 105 |

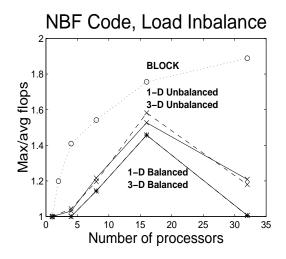

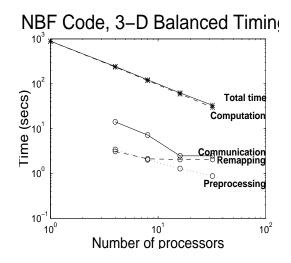

| 6.3  | The timing breakdown for nbf                               | 106 |

| 6.4  | The speedup for nbf                                        | 106 |

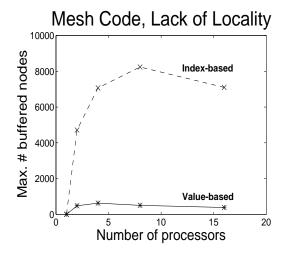

| 6.5  | The number of communicated data for the Mesh Code          | 108 |

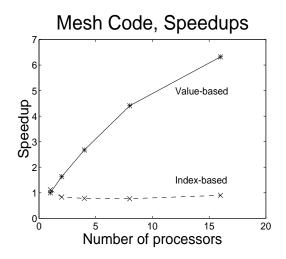

| 6.6  | The speedup for the Mesh Code                              | 108 |

| 6.7  | NAS CGM benchmark, subroutine matvec()                     | 108 |

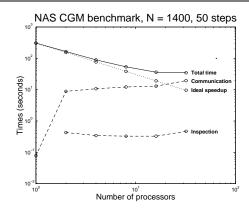

| 6.8  | Performance of Fortran D for the NAS CGM benchmark         | 110 |

| 6.9  | Performance of Gromos in Fortran D                         | 110 |

| 6.10 | F77 version of the non-bonded force calculation nbf        | 112 |

| 6.11 | $F90_{SIMD}$ version of nbf                                | 113 |

| 6.12 | Flattened F90 <sub>SIMD</sub> version of nbf               | 113 |

| 6.13 | CMFORTRAN/MPFORTRAN version of flattened nbf               | 116 |

| 6.14 | CMFORTRAN/MPFORTRAN version of unflattened nbf             | 118 |

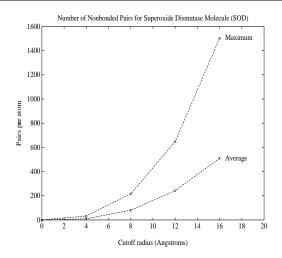

| 6.15 | Maximum and average number of non-bonded force interaction |     |

|      | partners per atom                                          | 120 |

| 6.16 | Performance results for the CM-2 and the DECmpp 12000      | 121 |

# Chapter 1

## Introduction

Data-parallel languages, such as HIGH PERFORMANCE FORTRAN (HPF) [KLS+94] and FORTRAN D [FHK+90], allow for a "machine independent parallel programming style," in which the applications programmer uses a dialect of a sequential language and annotates it with high-level data distribution information. From this annotated program, data-parallel compilers will generate codes in different native Fortran dialects for different parallel architectures. The target architectures of these compilers include both shared- and distributed-memory architectures and both MIMD and SIMD machines. The overall goal for the code generated by the data-parallel compiler is to have a performance which is, for most applications, relatively close to the performance of hand-written native code.

Section 7.2.2 briefly describes the main concepts of the FORTRAN D language. A prototype FORTRAN D compiler targeting distributed-memory architectures has had considerable success with regular problems [HHKT92, HKK+91, HKT91, HKT92b, Tse93]. The goal of this dissertation is to extend the applicability of data-parallel compilers into the domain of irregular problems.

## 1.1 Irregular Problems

The definition of when an application is irregular varies:

- A physicist might classify a computational problem by the degree of geometric simplicity and the variance of density of the underlying physical problem. An example of a regular problem under this metric is the calculation of a simple wave equation for a homogeneous rectangular problem domain, whereas mapping out the gravity potential for an expanding galaxy is certainly of irregular nature.

- An applied mathematician who sees the mathematical description of a problem may consider the sparsity of the data describing a particular instance of the

problem. Typical examples are finite-difference methods, which have a dense (regular) description, vs. finite-element methods, whose description is sparse due to the varying element sizes.

• A computer scientist is typically interested in the complexity of the data structures and access mechanisms needed to efficiently solve a problem; here we say "efficiently" because even irregular problems can usually be captured by very simple data structures, but not without wasting memory and/or processing power. Simple arrays, accessed directly, are typical for regular problems, whereas irregular applications may employ arrays with indirection vectors, pointers, linked lists, or quad trees, for example [SLY90].

We consider a problem to be irregular if its data access patterns are hard to analyze at compile time; *i.e.*, there is no obvious, simple parallelization and data distribution that gives good speedups and makes efficient use of processing power and the memory hierarchy. With increasing processor power opening the door to solving scientific problems that were previously impractical to solve ("Grand Challenges"), the relative importance of the already widespread irregular applications is expected to increase even further. Examples for areas of high interest are molecular dynamics, galaxy simulation, gene decoding, climate modeling, and computational fluid dynamics. Typical difficulties that arise from parallelizing irregular problems are summarized below:

**Difficulty 1** Poor load balance, for example when modeling a rapidly changing physical system.

**Difficulty 2** Lack of compile-time knowledge about where and which data have to be communicated, for example in Monte-Carlo processes.

**Difficulty 3** Limited locality, for example when computing long-range interactions between particles.

**Difficulty 4** Large communication requirements, for example when simulating many timesteps of a relatively small, but dynamic system.

#### 1.2 Previous Results

The compiler support level is the focus of this thesis. A principal reason for developing powerful compilers is to shift responsibilities for tedious low-level details away from

the programmer. This is typically associated with a tradeoff between abstraction and performance, which is unfortunate but can be justified to some degree. However, there also seems to be a fine line between a compiler being powerful and helpful, for example by assisting the programmer in dealing with machine-specific details, and a compiler trying to be too smart and getting in the way of the programmer. The virtual-machine model used by CM FORTRAN [BHMS91] can be seen as a typical example of the latter [Chr91], as explained in more detail in Chapter 4.

A programmer should not have to make this tradeoff when choosing a compiler, especially in a performance-oriented field such as scientific parallel computing. A compiler should try to assist the user in making some decisions, but it should also provide the user with convenient mechanisms to guide or override the compiler; such mechanisms are particularly important considering that parallelizing compiler technology is still in its infancy. Citing from a study about parallelizing different applications (including a molecular dynamics simulation) using the FX/FORTRAN parallelizing compiler [SH91]:

It is worth noting that the available directives were sometimes found to be restrictive or incapable of expressing the exact information we wished to convey to the compiler.

This observation has led to a trend away from completely automatic parallelizing compilers, which try to extract parallelism from a sequential program without any user assistance, towards the development of more annotation-oriented languages, which try to give the user a convenient interface for indicating parallelism. This approach is similar to the power steering paradigm [KMT91] used for loop transformations, where the compiler cannot always pick the best transformation, but it assists the user by (conservatively) testing correctness and performing the actual rewriting work. Developing annotations for conveying information to the compiler at a high level is a part of this dissertation.

#### 1.2.1 The inspector-executor paradigm

An important concept associated with communication optimization for applications using irregular array subscripts is the *inspector-executor* paradigm [MSS<sup>+</sup>88, KMV90, KMSB90, WSBH91]. A loop that contains indirect accesses to a distributed array is processed in four steps:

- 1. The *inspector* runs through the loop and only records which array elements are accessed, without doing the actual computation. *Communication schedules* are computed that satisfy the communication requirements induced by these access patterns.

- 2. A gather operation fetches all referenced off-processor data from their owners and buffers them locally.

- 3. The executor runs through the loop and performs the computation.

- 4. A *scatter* writes all off-processor data that have been defined in the loop back to their owners.

The inspector-executor paradigm has been shown to be very effective under certain circumstances and recently has been extended to general patterns of control flow [DSvH93, Das94].

#### 1.2.2 Compilation systems for irregular problems

Projects that have aimed at least to some degree towards compiler support for parallelizing irregular problems are the following.

#### Kali

Kali [KMV90, MV90, KM91] is the first compiler system that supports both regular and irregular computations on MIMD distributed-memory machines. Programs written for Kali must specify a virtual processor array and assign distributed arrays to Block, Cyclic, or user-specified decompositions. Instead of deriving a computational decomposition from the data decomposition, Kali requires that the programmer annotates each parallel loop with an ON clause that maps loop iterations onto the processor array. Communication is then generated automatically based on the ON clause and data decompositions. An inspector/executor strategy as described in Section 1.2.1 is used for run-time preprocessing of communication for irregularly distributed arrays [KMSB90]. Major differences between Kali and Fortran D include Kali's mandatory ON clauses for parallel loops and Fortran D's support for alignment, collective communication, and dynamic decomposition.

#### ARF

ARF is another compiler based on the inspector-executor paradigm. ARF is designed to interface FORTRAN application programs with the PARTI run-time routines described in Section 7.1.2 [WSHB91]. It supports BLOCK, CYCLIC, and user-defined irregular decompositions. The goal of ARF is to demonstrate that inspector/executors based on PARTI primitives can be automatically generated by the compiler.

#### Fortran S

FORTRAN S [BKP93] is a variation on FORTRAN 77 that contains directives for explicit parallelism. Conditioned Iterations Loops [HPE94] amortize the cost of irregular data accesses on distributed shared memory machines by first inspecting each iteration of a loop on whether a processor owns the page of data associated with it, and then looping explicitly over these iterations.

#### 1.2.3 Mapping arrays and mapping functions

To specify irregular mappings in a data-parallel context, index-based mapping arrays [WSBH91] or mapping functions [CMZ92] have been proposed. However, such arrays or functions that explicitly map indices to processors have to be provided by the programmer, even though she or he may not be interested in what exactly these mappings look like.

Another alternative is to replicate the data and distribute just the computation itself and combine results at the end. This approach has the further advantage of simplicity and robustness, and for relatively small problem sizes and numbers of processors it may actually result in satisfactory performance [CM90]. However, one of the main advantages of distributed-memory machines, scalability to large problem and machine sizes, has to be compromised under this approach. Alternatively, one may distribute the data in a way that considers the actual data dependences specific to their application [CHMS94]. These "irregular" mappings are typically harder to debug and manage than regular mappings and present an additional level of complexity beyond general message-passing style programming.

#### 1.2.4 Value-based mappings

Value-based distributions were initially proposed as an enhancement to FORTRAN 77D [Han92]. A variant of it, based on a GeoCoL (Geometrical, Connectivity and/or Load) data structure, has since then been implemented in a FORTRAN 90D prototype compiler by Ponnusamy et al. [PSC93a, PSC+93b]. However, the GeoCoL structure still has to be managed explicitly by the programmer.

#### 1.2.5 Communication analysis

Determining communication requirements and satisfying them efficiently is critical for any parallel program running on a distributed-memory machine. Eliminating redundant communication, message blocking and hoisting, and hiding communication delays are important optimizations, all of which are particularly difficult to perform for irregular problems. Our strategy for effective communication placement is based on an extensive data-flow framework.

Data-flow analysis is a common technique for reasoning at compile time about the run-time behavior of the program concerning variable definitions and uses. The bulk of the work in this field has treated all variables as scalars, resulting in a very conservative analysis for array variables. More precise methods are based on representations of array subsets, such as data access descriptors [Bal90] or regular sections [HK91].

The W2 compiler [GS90] for the Warp multiprocessor gathers information such as the set of definitions reaching a basic block to exploit the fine-grain parallelism offered by the highly pipelined functional units. It is based on interval analysis [All70, Coc70] and computes information with array region granularity.

Granston and Veidenbaum combine flow and dependence analysis to detect redundant global memory accesses in parallelized and vectorized codes [GV91]. They assume that the program is already annotated with READ/WRITE operations. Their technique tries to eliminate these operations where possible, also across loop nests and in the presence of conditionals.

What appeared to be lacking so far is a general approach towards analyzing the communication needs of a given program and determining when communication statements can be combined and hoisted. This dissertation contributes a data-flow framework which provides this analysis and furthermore gives specific treatment for the access patterns induced by irregular applications (see Chapter 3).

#### 1.2.6 Evaluation

The area of compiling regular applications onto distributed-memory machines has become very active, and much progress has been made. The formation of the HIGH PERFORMANCE FORTRAN Forum, an ongoing standardization effort for commercial parallel FORTRAN compilers, is certainly an indication for this progress. HPF derives many of its underlying concepts from FORTRAN D, which is the base language chosen for the extensions proposed here, and other languages, such as VIENNA FORTRAN [BCZ92].

The body of work that focuses on irregular applications is much smaller. In particular, there are few attempts to directly exploit the characteristics of underlying applications (such as the positions of atoms in a protein); previous approaches are commonly based on access patterns (such as a pairlist directly indicating the interaction partners for each atom) and try to determine data decompositions and communication optimizations after the access patterns of the program have been determined.

A compiler cannot reasonably be expected to derive all locality aspects of the application underlying a given program. However, there appears to be a considerable potential for optimizations if the user has a convenient way to express locality information to the compiler. The main objectives of this dissertation are the design and evaluation of language extensions that provide such an interface and the development of the compiler analysis necessary to support these extensions.

#### 1.3 The Thesis

The thesis of this dissertation is the following:

It is feasible and profitable to provide compiler support for the parallelization of scientific applications of an irregular nature to directly exploit the spatial locality of the underlying problem. An important component of this compiler support is the concept of value-based mappings which are derived from snapshots of the spatial configuration of the application. In combination with the distribution and alignment mechanisms provided in data-parallel languages such as FORTRAN D, value-based mappings are a practical and convenient handle for expressing both spatial locality and data interdependence.

Here, as in the rest of this dissertation, the term *spatial locality* refers to the physical locality in the problem domain of the application (as opposed to locality of reference

in an array, for example). Furthermore, the term *data interdependence* is used in a high-level sense, such as "the force between two particles depends on their distance" (as opposed to the field of dependence analysis which derives statement-ordering constraints based on definitions and uses of the same variables).

The goal for this dissertation is to validate this thesis and to show its effectiveness for handling irregular applications by extending the support for irregular problems within the FORTRAN D framework.

The rest of this thesis is organized as follows. Chapter 2 introduces value-based mappings, which are an extension of FORTRAN D to express spatial locality when distributing data across processors. Chapter 3 describes GIVE-N-TAKE, a code placement framework which the FORTRAN D compiler uses to place communication statements. Chapter 4 addresses some SIMD-specific issues when parallelizing irregular applications and develops the *loop-flattening* transformation. Chapter 5 describes practical aspects of the FORTRAN D implementation, followed by experimental results in Chapter 6. Chapter 7 provides a more comprehensive treatment of background and related work. Chapter 8 presents conclusions, open problems, and future work. In addition, Appendix A proves the correctness of the GIVE-N-TAKE framework from Chapter 3.

He was to leave inhabited districts behind and begin a trek tailor-made for disaster, given his propensity for getting lost at the best of times.

His guides, on taking their leave, cheerfully advised him to recite the sacred texts from time to time to avoid being eaten by snow leopards.

— Scott Berry (A Stranger in Tibet - The Adventures of a Zen Monk)

# Chapter 2

# Value-Based Mappings

Let us assume that the value assigned to some array element a(i) depends on some other array element b(j). In a regular problem, there will typically be some simple relationship between i and j; for example, they may be related to each other via a linear function known at compile time. This usually implies that at least this dependence can be satisfied, with little or no communication, when a and b are distributed by first partitioning their index spaces in some regular fashion among processors and then aligning them to each other in a certain way. We will refer to this characteristic as index-based locality. Exactly how arrays should be mapped in the presence of index-based locality is by no means trivial and still an active field of research [KMCKC93]. However, one can generally assume that only regular mappings (such as BLOCK, CYCLIC, or BLOCK\_CYCLIC) and remappings need to be considered.

For irregular problems, this assumption cannot be made. Here subscripts i and j may each be determined by some complicated function or an array lookup, whose outcome is unknown at compile time. Furthermore, even if the compiler knew the values of the is and is, there would often still be no way to achieve good locality (i.e., low communication requirements) via regular, index-oriented mappings. For example, if i and j are different vertices in a mesh, then a(i) and b(j) might depend on each other if i and j are linked together by an edge. Most meshes number their vertices in a way that does not directly reflect their topology; i.e., it is hard to predict whether two vertices are linked together by just looking at their indices. Therefore, distributing mesh points and the computation associated with them across processors by dividing their index space in some regular fashion typically results in many offprocessor accesses; i.e., if a processor is assigned some a(i) and therefore has to know the value of b(j), chances are high that b(j) will be on a different processor. The potential speedup gained from distributing data and computation across processors is likely to be lost by exceedingly high communication costs when using simple mapping schemes.

The fact that the vertex numbering does not reflect the mesh topology is an example of poor index locality within a data structure, which we consider a data distribution problem. However, we may also have bad locality across data structures. Revisiting the mesh example, we are typically operating on vertices and edges, which have a certain interrelationship (each edge has two particular vertices as end points). This relationship can usually not be determined from the node and edge numbering. However, it would generally be advantageous if the data associated with an edge would be stored on the same processor as the data associated with its end points; we consider this a data alignment problem.

Fortunately, many scientific applications lacking any index-based locality that a compiler might take advantage of do offer another kind of locality, which we will refer to as *value-based locality*. This kind of locality, which will be introduced in more detail in the next section, naturally lends itself to *value-based mappings*. These mappings can be used to improve locality and also to increase load balance.

The rest of this chapter is organized as follows. Section 2.1 introduces value-based locality and illustrates the use of value-based mappings with kernels taken from a molecular dynamics code and an unstructured mesh application. (Experimental results obtained for these kernels are contained in Section 6.1.) Section 2.2 lists the implications of value-based mappings for message-passing node programs. Section 2.3 describes language extensions and compiler technology for generating such node programs. (A comparison of the effectiveness of index-based and value-based mappings for these applications is presented in Section 6.1 as well.)

## 2.1 Value-Based Locality

In the presence of value-based locality, two array references a(i) and b(j) may not be related to each other via their indices i and j, but instead by their values a(i) and b(j), or by the values of other variables, such as x(k) and x(l), that in turn are related to a(i) and b(j) by their indices (for example, k = i and l = j). In this context, "related" refers to a preference towards residing close to each other with respect to the memory hierarchy, e.g., on the same processor. Revisiting the mesh example, x might be a coordinate array storing the physical location of each mesh point (assuming 1-D for simplicity). Then the probability that vertices i and j are connected increases as |x(i) - x(j)| decreases. Note that this is not a strict relationship; whether an edge actually exists or not still depends on other factors, such as mesh density and

topology. However, since data mapping is not a correctness but only an efficiency issue, we are usually more interested in a fast heuristic for finding a reasonably good data mapping than in a strictly optimal, but expensive solution.

Value-based mappings allow the programmer to express value-based locality as a simple extension of the regular mapping mechanism employed in data-parallel languages. We distinguish between value-based distributions and value-based alignments. For example, let array  $\mathbf{x}$  be aligned to a decomposition arrayD. Then the directive DISTRIBUTE arrayD(VALUE( $\mathbf{x}$ )) is a value-based distribution specifying that decomposition arrayD (and with it array  $\mathbf{x}$ ) should be distributed such that the values of the elements of  $\mathbf{x}$  assigned to each individual processor are from disjoint intervals. (See Section 2.3.1 for a more formal description of the syntax proposed for value-based mappings.) In other words, if the values of two elements of some array elements  $\mathbf{x}$ ( $\mathbf{i}$ ) and  $\mathbf{x}$ ( $\mathbf{j}$ ) are close, then  $\mathbf{x}$ ( $\mathbf{i}$ ) and  $\mathbf{x}$ ( $\mathbf{j}$ ) are likely to be mapped to the same processor, no matter what relationship  $\mathbf{i}$  and  $\mathbf{j}$  may have to each other.

#### 2.1.1 Molecular dynamics - An example for value-based distributions

Examples where data are not related by indices, but by values, are molecular dynamics programs such as Gromos [GB88], CHARMM [BBO<sup>+</sup>83], or ARGOS [SM90] that are used to simulate biomolecular systems. One important routine common to these programs is the non-bonded force (NBF) routine, which typically accounts for the bulk of the computational work (around 90%). Figure 2.1 shows an abstracted version of a sequential NBF calculation. An important characteristic of NBFs is that their intensities decay very rapidly with increasing distance between the atoms involved. This locality is exploited by using a cutoff radius,  $R_{cut}$ , beyond which the NBF interactions are ignored. This reduces the number of atom pairs for which the NBF has to be computed and significantly reduces overall computational costs. Furthermore, we can exploit this locality when distributing data in a parallel implementation according to the values of x, which stores the physical atom coordinates. The atom numbering itself is not related to the coordinates; instead, they are typically numbered according to some data bank standard, such as the Brookhaven protein data bank, which considers amino acid types, peptide bonds, solute/solvent classifications, etc. – an ordering which is rather difficult for a compiler to take direct advantage of without user assistance. Therefore, a traditional, index-based mapping would lose this locality. In fact, since each processor needs for each owned atom to

```

\begin{aligned} \textbf{do} \ i &= 1, N_{atom} \\ \textbf{do} \ p &= 1, inb(i) \\ j &= partners(i, p) \\ force &= nbf\_func(x(i), x(j)) \\ f(i) &= f(i) + force \\ f(j) &= f(j) - force \\ \textbf{enddo} \\ \textbf{enddo} \end{aligned}

```

Figure 2.1 Sequential version of the Non-Bonded Force kernel  $\mathtt{nbf}$ .  $N_{atom}$  is the total number of atoms, inb(i) is the number of atom partners that are close enough to atom i to be considered for the NBF calculation. For simplicity, the coordinate and force arrays x and f are shown only one-dimensional.

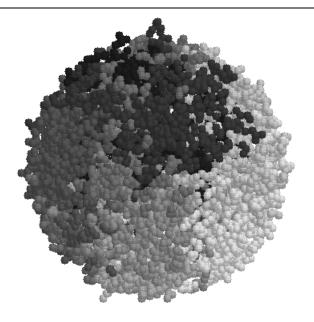

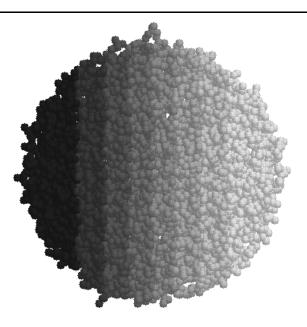

know about all atoms within  $R_{cut}$  of that atom, a regular mapping typically results in each processor accessing all data, with accordingly high communication and storage requirements. For example, Figure 2.2 shows the mapping resulting from distributing an SOD\* system ( $N_{atom} = 6968$ ) across eight processors.

The actual use of a value-based distribution can be seen in Figure 2.3, which shows a FORTRAN D implementation of the nbf kernel outlined in Figure 2.1. This program is a condensed and abstracted version of the 340-line GROMOS subroutine nonbal.f, enhanced with some data initialization. Although this program is very simplified, it still presents similar difficulties as the original code with respect to the compiler. FORTRAN D directives first declare a decomposition atomD (line 10), then align coordinates x, forces f, partner counts inb, and adjacency lists partners with atomD (line 11), and finally distribute atomD. Note that initially this is a regular, BLOCK-wise distribution (line 12). After reading in the initial coordinates and partner counts (line 15), atomD gets redistributed according to the values of coordinate array x (line 18). Note also that the strict owner-computes rule is overridden in the NBF calculation itself via an ON\_HOME directive (line 29). Figures 2.4 and 2.5 show the SOD mappings resulting from one- and three-dimensional value-based mappings, respectively.

<sup>\*</sup>SOD (superoxide dismutase) is a catalytic enzyme that converts the toxic free-radical,  $O_2^{-4}$ , a byproduct of aerobic respiration, to the neutral molecules  $O_2$  and  $H_2O_2$  [WCSM93].

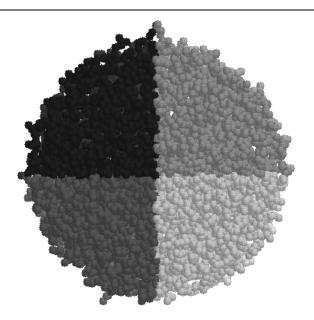

Figure 2.2 BLOCK mapping of an SOD system. Atoms are shaded according to the processor they are mapped to, for an eight-processor configuration. The regular, index-based mapping results in assigning each processor very irregular subdomains, with accordingly poor locality and load balance.

#### 2.1.2 Unstructured meshes - An example for value-based alignments

An example of a value-based alignment is shown in Figure 2.6, which shows a FORTRAN D version of a sweep over the edges of an unstructured mesh [Mav91]. There are two decompositions, nodeD for the node data and edgeD for the edge data. After reading in the data (line 15), first nodeD gets distributed by value according to the node coordinates; that is, the values of x determine the mapping of node data indices onto processors (line 18). Secondly, edgeD gets aligned with nodeD according to the values of the topology arrays ends1 and ends2 (line 21); that is, the edge-index-to-node-index mappings given by ends1 and ends2 are combined with the node-index-to-processor mapping of nodeD. Note that since edges tend to connect nodes that are relatively close together, one would expect the two composed mappings, which correspond to the both endpoints of each edge, to agree in most cases. However, there may be conflicts in which case heuristics have to be used, which might for example keep load balancing in mind or simply toss a coin.

```

PROGRAM nbf

INTEGER i, j, p, t, n$proc, Natom, pMax, Nstep

PARAMETER (n$proc = 8)

PARAMETER (Natom = 8000, pMax = 250, Nstep = 30)

5

INTEGER inb(Natom), partners(Natom, pMax)

REAL x(Natom), f(Natom), force, nbf_func, delta_func

FORTRAN D directives

10

DECOMPOSITION atomD(Natom)

ALIGN inb, x, f, partners(i,j) WITH atomD(i)

DISTRIBUTE atomD(BLOCK)

С

Initialize data

CALL read_data(x, inb, partners)

15

С

Redistribute atomD according to coordinate values

DISTRIBUTE atomD(VALUE(DIM=1, VALS=x, WEIGHT=inb))

20 C

Loop over time steps

DO t = 1, Nstep

С

Reset forces to zero

DO i = 1, Natom

f(i) = 0

^{25}

ENDDO

Computes forces

EXECUTE (i) ON_HOME f(i)

30

DO i = 1, Natom

DO p = 1, inb(i)

j = partners(i, p)

force = nbf_func(x(i), x(j))

f(i) = f(i) + force

f(j) = f(j) - force

35

ENDDO

ENDDO

Push atoms

С

40

DO i = 1, Natom

x(i) = x(i) + delta_func(f(i))

ENDDO

ENDDO

END

```

Figure 2.3 FORTRAN D version of the Non-Bonded Force kernel (with coordinates and forces shown 1-D for simplicity). During each of the Nstep time steps, forces are first reset to zero, then they are computed based on the distances between atoms (similar to the code in Figure 2.1), and finally the forces are used for updating coordinates. Note the index-based distribution directive in line 12, followed by a value-based redistribution in line 18.

Figure 2.4 Value-based mapping of atoms along just one dimension. Locality is good, but communication may be expensive due to the high surface-to-volume ratio.

Figure 2.5 Value-based mapping of atoms along all three dimensions. Locality is good, and the compact subdomains minimize communication costs.

```

PROGRAM mesh

INTEGER i, n1, n2, n$proc, Nnodes, Nedges, Nstep, t

PARAMETER (n$proc = 8, Nnodes = 10000, Nedges = 20000)

INTEGER ends1(Nedges), ends2(Nedges)

5

REAL x(Nnodes), f(Nnodes), w(Nnodes), flux

С

FORTRAN D directives

DECOMPOSITION nodeD(Nnodes), edgeD(Nedges)

ALIGN f, w, x, WITH nodeD

10

ALIGN ends1, ends2 WITH edgeD

DISTRIBUTE nodeD(BLOCK), edgeD(BLOCK)

С

Initialize data

CALL read_data(x, w, ends1, ends2)

15

С

Redistribute nodeD according to coordinate values

DISTRIBUTE nodeD(VALUE(DIM=1, VALS=x))

Redistribute edgeD according to nodeD

20 C

ALIGN egdeD WITH nodeD(VALUE(DIM=2, VALS=ends1,ends2))

Loop over time steps

DO t = 1, Nstep

^{25}

С

Reset fluxes to zero

DO i = 1, Nnodes

f(i) = 0

ENDDO

С

Computes fluxes

EXECUTE (i) ON_HOME ends1(i)

DO i = 1, Nedges

n1 = ends1(i)

n2 = ends2(i)

35

flux = flux_func(w(n1),w(n2))

f(n1) = f(n1) + flux

f(n2) = f(n2) + flux

ENDDO

ENDDO

40

END

```

Figure 2.6 FORTRAN D kernel of a sweep over the edges of an unstructured mesh. The mesh coordinates are stored in the coordinate array x (again 1-D for simplicity), the topology is stored in the endpoint arrays ends1 and ends2. After an initial index-based distribution of node and edge data in line 12, the node data are redistributed by value in line 18, and edge data are aligned by value with the redistributed node data in line 21.

| i | $\mathbf{x}(i)$ | $\mathtt{nodeD}(i)$ | $\mathtt{ends1}(i)$ | $\mathtt{ends2}(i)$ | $\mathtt{edgeD}(i)$ |

|---|-----------------|---------------------|---------------------|---------------------|---------------------|

| 1 | 1.0             | 0                   | 1                   | 3                   | 0                   |

| 2 | 4.8             | 1                   | 3                   | 4                   | 1                   |

| 3 | 3.8             | 1                   | 2                   | 3                   | 1                   |

| 4 | 2.5             | 0                   | 1                   | 4                   | 0                   |

| 5 | -               | _                   | 2                   | 4                   | 1                   |

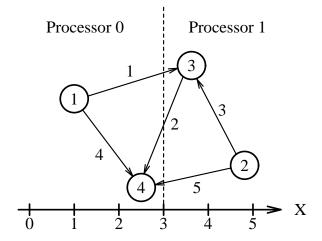

Figure 2.7 Example mesh with four nodes and five edges. The table shows its node coordinates (x), topology (ends1, ends2), and resulting mappings (nodeD, edgeD) for two processors.

A simple example where four nodes and five edges are mapped onto two processors is shown in Figure 2.7. Given the mesh code in Figure 2.6, the FORTRAN D compiler will generate code that at the location of the value-based mapping directive in line 18 will call a partitioner; see also Section 2.3.2. This partitioner will determine at run time a function which maps the values stored in  $\mathbf{x}$ , which represent physical coordinates in space, to processors. A mapping function preserving physical locality and load balance would be, for example,

$$f_{nodeD}(x) = \begin{cases} 0 \text{ if } x \le 3, \\ 1 \text{ if } x > 3. \end{cases}$$

This corresponds a distribution function which maps array indices to processors as follows:

$$\mathtt{nodeD}(i) = \left\{ \begin{array}{l} 0 \text{ if } \mathbf{x}(i) \leq 3, \\ 1 \text{ if } \mathbf{x}(i) > 3. \end{array} \right.$$

After mapping node data to processors, edge data are mapped (line 21), preferably to the same processors on which the node data of the endpoints of each edge are residing. As mentioned in the previous paragraph, there may be mapping conflicts if the endpoints of the same edge are on different processors. In Figure 2.7, edges are shown directed to distinguish between the endpoints given by ends1 (tail) and ends2 (head). In this example, let us assume for simplicity that such conflicts, which occur for edges 1, 2, and 5, are resolved by favoring the processor to which the tail node (ends1) is mapped to. This corresponds to a mapping function

$$edgeD(i) = nodeD(ends1(i)).$$

## 2.2 Implications of Value-Based Mappings

The prototype MIMD FORTRAN D compiler transforms a FORTRAN D program, written in a global name space and annotated with data mapping directives, into a message-passing program, which is a local name space node program including communication statements. This section describes the effect that distributing data by value has on a node program which may be generated by the compiler or coded by a programmer directly using message passing.

#### 2.2.1 Specification and state

A regular distribution can be fully specified by a simple keyword ("BLOCK"), or a keyword enhanced with a small list of parameters ("BLOCK\_CYCLIC(blockSize)"). There is very little state associated with a mapping, both at compile time and at run time. This already implies some simplicity for the programming assignment and for the resulting program. Many mapping-dependent decisions, such as the effect of an owner-computes rule (which links the mapping of computation to the mapping of the data involved), can already be resolved before run time. The amount of additional code and variables for computing and storing the mappings and for translating between global indices, local indices, and processor numbers is very small.

If an application has good index-based locality, then an irregular distribution may be used to improve load balance, but some or all of the mapping computation can still be done on the fly [BK93, Bia91, CHMS94]. Given a value-based distribution (i.e., assuming no index-based locality), which for example distributes  $\mathbf{x}$  according to its values, one could envision a scheme that also had very little state specifically devoted to representing the distribution. For example, one could compute the owner of some  $\mathbf{x}(\mathbf{i})$  on the fly by sorting all elements of  $\mathbf{x}$  and determining the position of  $\mathbf{x}(\mathbf{i})$  in the sorted list. This, however, would clearly be impractical to do for each reference to an element of  $\mathbf{x}$ . Instead, one should amortize the cost of determining ownership etc. by computing this information once and reusing it.

However, representing a value-based distribution explicitly requires a large amount of state. A translation table maps global indices  $i_{glob}$  into pairs  $(i_{loc}, p)$  of local indices and processor numbers. Often the translation table itself is too large to be fully replicated and is distributed instead [WSBH91]. Therefore, not only storing but also accessing the information adds complexity to the program. As also described in Section 7.1.2, run-time libraries such as Chaos can take most of the complexity of this task from the programmer [DHU+93], but their use still requires explicit managing of the data structures associated with irregular distributions and communications.

#### 2.2.2 Storing value-based distributed data

Again assuming that **x** is distributed according to its value, the number of elements of **x** assigned to each processor typically varies and is not known until run time. This poses particular problems when using a language that does not support dynamic memory allocation, such as FORTRAN 77. Common strategies for circumventing this

restriction are to make arrays conservatively large or declare work arrays that are shared by several variables, both of which have obvious disadvantages.

Note that the same problem occurs when regularly distributed arrays are accessed irregularly and we wish to append buffer space for off-processor data at the end of the array [Han93].

#### 2.2.3 Translating name spaces

Translating between the global name space of a FORTRAN D program and the local name space of the node program is an important component of the parallelization process. For regular mappings, most of this task can be performed before run time, or, if run-time translation is needed, the necessary code can be generated fairly easily; for example, a statement x(i) = i, where i is global, might be translated into something like  $x(i) = i + my proc*block_size$ , with a local i.

For irregular mappings, the translation has to be delayed until run time, and computing the translation may be complicated.

#### 2.2.4 Communication generation

Again due to the complicated relationship between global and local name spaces, generating correct communication statements in the presence of value-based mappings can be tricky for regular array accesses, such as x(i) = x(i+1), and even more so for irregular references, such as x(a(i)) = x(b(i)).

Resolving such references requires several translation steps, some of which may themselves involve communication. To still generate efficient code, one should precompute and reuse as much of this information as possible. The *inspector-executor* paradigm (Section 1.2.1) allows us to message-vectorize low-locality data accesses, even in the absence of compile-time knowledge.

#### 2.2.5 A bootstrapping problem

One characteristic of value-based mappings is that they may pose a certain bootstrapping problem to both the user and the compiler, as has also been identified by Ponnussamy et al. [PSC93a]. This problem occurs when an array is distributed based on its own values, which is considered perfectly legal, as is the case in the code shown in Figure 2.3. Here an array  $\mathbf{x}$  is aligned to a decomposition  $\mathbf{atomD}$ , which in turn gets distributed based on the values of  $\mathbf{x}$ . When we start initializing  $\mathbf{x}$ , we need to

know its mapping function to assign each processor its share of array elements. This mapping function, however, cannot be determined until we know all values of x.

To resolve this problem, we start out with a different, typically regular mapping, which can be used for example to read in the data as is the case with the program shown in Figure 2.3. After the data relevant for the irregular mapping are known, the decomposition is remapped based on their values.

#### 2.3 The Compiler's Perspective

The previous section outlined the general issues associated with distributing data based on values. This section addresses some of the implications of using value-based mappings in the context of a data-parallel language such as FORTRAN D. A more detailed discussion of the implementation aspects of value based mappings can be found in Chapter 5.

#### 2.3.1 The input language

Since we implemented value-based mappings as part of a FORTRAN D compiler prototype, the FORTRAN D language constructs also serve as a basis for the syntax of value-based mappings. These extensions could also be applied directly to the HPF standard [KLS+94]. We were able to limit ourselves to a simple extension of the already existing DISTRIBUTE and ALIGN directives, as was also illustrated by the code in Figure 2.3. Here the directive DISTRIBUTE atomD(VALUE(DIM=1, VALS=x, WEIGHT=inb)) was the only statement the programmer had to add in order to express the value-based locality of the application; the rest was done by the compiler. The value-based mapping syntax currently supported is shown in Figure 2.8.

Note that the range of available mapping strategy depends more on the available run-time support than on the compiler. In fact, the strategy specified by the user might be passed through verbatim to the run-time library. However, one might still require a certain minimal set of strategies to be always available [Han89, PSC93a].

Note also that the user may not select a specific strategy for distributing data explicitly, as shown in Figure 2.3. In this case the compiler chooses a default strategy, such as recursive bisection [BP90] or spacefilling curves [PB94]. Furthermore, since the default number of dimensions is one and some key words are optional, the DISTRIBUTE atomD(VALUE(DIM=1, VALS=x, WEIGHT=inb)) could be abbreviated as DISTRIBUTE atomD(VALUE(x,inb)).

```

DistDirective is DISTRIBUTE ValMapping

AlignDirective is ALIGN decomposition-name WITH ValMapping

ValMapping is decomposition-name (VALUE (ValArrays [, Weight] [,Strategy]))

ValArrays is [DIM = num-dims,] [VALS =] val-array-name [, val-array-name] ...

Weight is [WEIGHT =] weight-array-name

Strategy is [STRATEGY =] mapping-strategy-name

Constraint: Number of val-array-names must be one, or, if specified, num-dims.

```

Figure 2.8 Syntax of the value-based mapping directive. Square brackets indicate optional components.

Naturally, there are several possible modifications/extensions for this syntax, which was held deliberately simple. For example, the value-based alignments could also be expressed as just another form of redistributions instead. Or, one could allow multidimensional value arrays instead of several one-dimensional arrays; for example, a program may store three-dimensional physical coordinates in one two-dimensional array, x(3, n), instead of using three one-dimensional arrays, x(n), y(n), z(n).

#### 2.3.2 When to distribute and align

In general, mapping directives can be viewed as either static declarations (such as the HPF DISTRIBUTE), or as executable statements (such as the HPF REDISTRIBUTE). There are several reasons why value-based mappings should be viewed as executable, for example because of the bootstrapping problem described in Section 2.2.5, or because the values relevant for the mapping might change for dynamic problems and we might want to remap periodically.

A resulting question is when this mapping should be performed, whether it should be done when the execution reaches the directive, or instead at some other point in the program determined by the compiler. In the latter case, one might for example envision a scheme that lets the compiler analyze where relevant values are defined (or redefined) and where mapped data are used. However, the gain in programming convenience appears to be only marginal, and this kind of analysis seems to be fairly difficult and problem dependent; for example, we might not really want to redistribute

whenever one relevant value changes. Therefore, the current implementation performs the value-based mappings at the location corresponding to the mapping directive (see also Section 5.3.2).

Value quietness, in which one has no wandering desires at all but simply performs the acts of his life without desire, that seems the hardest.

— Robert M. Pirsig (Zen and the Art of Motorcycle Maintenance)

## Chapter 3

# Balanced Code Placement with Give-N-Take

The previous chapter introduced the concept of value-based mappings to provide an efficient mechanism for specifying irregular data distributions with good locality and equalized work loads. However, in most cases even the best distribution results in some off-processor accesses; *i.e.*, the program requires communication. In the nbf example program in Figure 2.3, the communication steps are gathering coordinates and scattering forces. A performance-critical task of the compiler is to minimize the overheads associated with communication by generating and placing the communication statements judiciously. This requirement motivated the development of the GIVE-N-Take data-flow framework described in this chapter. As it turns out, however, communication placement is only one of the possible application of this framework, which for example can be used for any code placement task that is traditionally solved by Partial Redundancy Elimination (PRE).

The rest of this chapter is organized as follows. Section 3.1 revisits PRE and analyzes some of its current limitations. Section 3.2 introduces the communication generation problem, which will be used as an illustrating example application of GIVE-N-TAKE. Section 3.3 provides further intuition for the GIVE-N-TAKE framework and some background on the type of flow graph and neighbor relations used by the GIVE-N-TAKE equations. Section 3.4 states the actual equations and argues informally for their correctness and efficiency. Section 3.5 gives an efficient algorithm for solving the GIVE-N-TAKE equations. Section 3.6 concludes with a brief summary. Formal correctness proofs of GIVE-N-TAKE can be found in Appendix A.

## 3.1 Partial Redundancy Elimination

PRE is a classical optimization framework for moving and placing code in a program. Example applications include common subexpression elimination, loop invariant code motion, and strength reduction. The original PRE framework was developed by Morel and Renvoise [MR79] and has since then experienced various refinements [JD82, DS88,

Dha88a, Dha91, DRZ92, KRS92]. However, the PRE frameworks developed to date still have certain limitations, which become apparent when trying to apply them to more complex code placement tasks.

Atomicity: PRE implicitly assumes that the code fragments it moves, generates, or modifies are atomic in that they need only a single location in the program to be executed. For example, when placing the computation of a common subexpression, PRE will specify only one location in the program, and code will be generated at that location to perform the entire computation. Later optimizations may then reschedule the individual instructions, for example to hide memory access delays, but PRE itself does not provide any such mechanism.

Ignoring side effects: Taking again the example of common subexpression elimination, classical PRE assumes that each common subexpression has to be computed somewhere; *i.e.*, nothing "comes for free." However, there are problems where side effects of other operations can eliminate the need for actual code placement. For example, when placing register loads and stores, certain loads may become redundant with previous definitions. This is generally treated as a special case, for example by developing different, but interdependent sets of equations for loads and stores [Dha88b].

Pessimistic loop handling: One difficulty with flow analysis has traditionally been the treatment of loop constructs that allow zero-trip instances, such as a Fortran do loop. Hoisting code out of such loops is generally considered unsafe, as it may introduce statements on paths where they have not existed before. However, unless the computation to be moved may change the meaning of the program, for example by introducing a division by zero, we often would like to hoist computation out of such loops even if the number of iterations is not known at compile time.

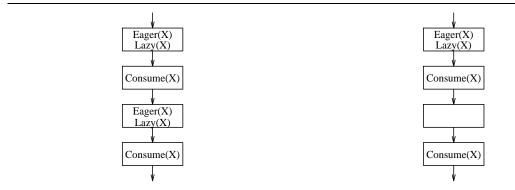

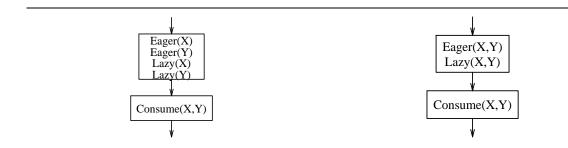

GIVE-N-TAKE aims to overcome these limitations in a general context. It is applicable to a broad class of code generation/placement problems, including the classical domains of PRE techniques as well as memory hierarchy related problems, such as prefetching and communication generation. GIVE-N-TAKE is subject to a set of correctness and optimality criteria as described in Section 3.3.2; for example, each consumption *must* be preceded by a production, and any generated code *should*

be executed as infrequently as possible. However, the solutions computed by GIVE-N-Take vary depending on which kind of problem it is applied to. In a Before problem, items have to be produced before they are needed (e.g., for fetching an operand), whereas in an After problem, they have to be produced afterwards (e.g., for storing a result). Intuitively, one can think of an After problem as a Before problem with reversed flow of control.

Orthogonally we can classify a problem as EAGER when it asks for production as early as possible (e.g., sending a message), or as LAZY when it wants production as late as possible (e.g., receiving a message); this definition assumes a BEFORE problem. For an AFTER problem, "early" and "late" have to be interchanged since we are reversing the graph. Classical PRE, for example, can be classified as a LAZY-BEFORE problem. This means that the same framework can be used for different flavors of problems; there are no separate sets of equations for loads and stores [Dha88b], or for READS and WRITES [GV91].

## 3.2 A Code Placement Example Problem: Communication Generation

An example of code placement is the generation of communication statements when compiling data-parallel languages, such as HIGH PERFORMANCE FORTRAN [KLS+94] or FORTRAN D [HKT92a]. For example, a processor of a distributed-memory machine may reference owned data, which by default reside on the processor, as well as non-owned data, which reside on other processors. Local references to non-owned data induce a need for communication, in this case a fetch of the referenced data from other processors. We will refer to such a fetch of non-owned data as a READ operation. Figure 3.1 shows another, simple example node code containing references to distributed data.